# PACE1750AE SINGLE CHIP, 20MHz to 40MHz, ENHANCED CMOS 16-BIT PROCESSOR

## FEATURES

- Implements the MIL-STD-1750A Instruction Set Architecture

- Single Chip PACE Technology<sup>™</sup> CMOS 16-Bit Processor with 32 and 48-Bit Floating Point Arithmetic

- Form-Fit-Functionally Compatible with the P1750A

- DAIS Instruction Mix Execution Performance Including Floating Point Arithmetic

- 1.8 MIPS at 20 MHz

- 2.7 MIPS at 30 MHz

- 3.6 MIPS at 40 MHz

- Conventional Integer Processing Mix Performance

- 5.0 MIPS at 40 MHz

- Power BIF Instructions Allow for High Throughput Implementations of Transcedental Functions, Navigational Algorithms and DSP Functions

- Inner Dot Product Instruction for 3X3, 16 Bit Registers in 150ns (2 clocks per Multiply/ Accumulate step) with 32 Bits Result

- Multiply/Accumulate Instructions for 32 Bit Registers is 200ns at 40MHz (8 clocks), with 48 Bit Result

- Parameteric Memory Inner-Dot Products for

# GENERAL DESCRIPTION

The PACE1750AE is a general purpose, single chip, 16bit CMOS microprocessor designed for high performance floating point and integer arithmetic, with extensive real time environment support. It offers a variety of data types, including bits, bytes, 16-bit and 32-bit integers, and 32-bit and 48-bit floating point numbers. It provides 13 addressing modes, including direct, indirect, indexed, based, based indexed and immediate long and short, and it can access 2 MWords of segmented memory space (64 KWords segments).

The PACE1750AE offers a well-rounded instruction set with 130 instruction types, including a comprehensive integer, floating point, integer-to-floating point and floating point-to-integer set, a variety of stack manipulation instructions, high level language support instructions such as Compare Between Bounds and Loop Control Instructions. It also offers some unique instructions such as vectored I/O, supports executive and user modes, and provides an escape mechanism which allows user-defined instructions, using a coprocessor.

- Fast Polynomial expansion algorithms

- Fast context switching with Instruction to block move up to 16 new mapping memory page registers

- 20, 30, and 40 MHz Operation over the Military Temperature Range

- Extensive Error and Fault Management and Interrupt Capability

- 26 User Accessible Registers

- Single 5V ± 10% Power Supply

- Power Dissipation over Military Temperature Range

- <0.5 watts at 20 & 30 MHz <1.0 watts at 40 MHz

- TTL Signal Level Compatible Inputs and Outputs

- Multiprocessor and Co-processor Capability

- Two programmable Timers

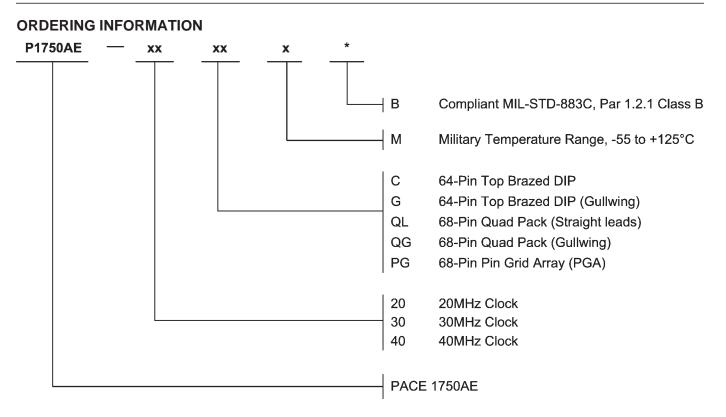

- Available in:

- 64-Pin Top Brazed DIP

- 68-Pin Pin Grid Array (PGA)

- 68-Lead Quad Pack (Leaded Chip Carrier)

The chip includes an array of real time application support resources, such as 2 programmable timers, a complete interrupt controller supporting 16 levels of prioritized internal and external interrupts, and a faults and exceptions handler controlling internally and externally generated faults.

The microprocessor achieves very high throughput of 3.6 MIPS for a standard real time integer/floating point instruction mix at a 40 MHz clock. It executes integer Add in 0.1  $\mu$ s, integer Multiply in 0.1  $\mu$ s, Floating Point Add in 0.45  $\mu$ s, and Floating Point Multiply in 0.225  $\mu$ s, for register operands at a 40 MHz clock speed.

The PACE1750AE uses a single multiplexed 16-bit parallel bus. Status signals are provided to determine whether the processor is in the memory or I/O bus cycle, reading and writing, and whether the bus cycle is for data or instructions.

Document # MICRO-2 REV G

Revised October 2005

## DIFFERENCES BETWEEN THE PACE1750A AND PACE1750AE

The PACE1750AE achieves a 41% boost in performance (in clock cycles) over the PACE1750A. This reduction in clocks per instruction is because of three architectural enhancements:

- 1) The inclusion of a 24 x 24 Multiply Accumulate (MAC) array.

- 2) A reduction in non-bus cycles to 2 clocks (bus cycles remain at 4 clocks to maintain full compatibility with CPU's peripheral chips).

- 3) Branch calculation logic.

The table below shows how the MAC improves all multiply operations — both integer and floating point — by 477% to 760%.

|                                            | PAC    | E1750AE                    | PA     | CE1750A                    |                     |

|--------------------------------------------|--------|----------------------------|--------|----------------------------|---------------------|

| Instruction                                | Clocks | Execution<br>Time (40 MHz) | Clocks | Execution<br>Time (40 MHz) | Gain<br>#Clocks (%) |

| Integer Add/Sub                            | 4      | 100ns                      | 4      | 100ns                      | —                   |

| Double Precision Integer Add/Sub           | 6      | 150ns                      | 9      | 225ns                      | 50                  |

| Integer Multiply                           | 4      | 100ns                      | 23     | 575ns                      | 575                 |

| Double Precision Integer Add/Sub           | 9      | 225ns                      | 69     | 1725ns                     | 760                 |

| Floating Add/Sub                           | 18     | 450ns                      | 28     | 700ns                      | 55                  |

| Extended Floating Add/Sub                  | 34     | 850ns                      | 51     | 1225ns                     | 50                  |

| Floating Multiply                          | 9      | 225ns                      | 43     | 1075ns                     | 477                 |

| Extended Floating Point Multiply           | 17     | 425ns                      | 96     | 2400ns                     | 564                 |

| Branch (Taken)                             | 8      | 200ns                      | 12     | 300ns                      | 50                  |

| Branch (Not Taken)                         | 4      | 100ns                      | 4      | 100ns                      | —                   |

| Flt'g' Point Polynomial Step (Mul+Add/Sub) | 27     | 675ns                      | 71     | 1775ns                     | 263                 |

| Ext Flt'g' Point Polynomial Step (Mul/Sub) | 51     | 1275ns                     | 147    | 3675ns                     | 2400                |

| DAIS Mix (MIPS)                            | —      | 3.56                       |        | 2.52                       | 41/59               |

## PACE1750AE BUILT IN FUNCTIONS

A core set of additional instructions have been included in the PACE1750AE. These instructions utilize the Built In Function (BIF) opcode space. The objective of these new opcodes is to enhance the performance of the PACE in critical application areas such as navigation, DSP, transcendentals and other LINPAK and matrix type instructions. Below is a list of the BIFs and their execution times (N = the number of elements in the vector being processed).

| Instruction                          | Mnemonic | Address<br>Mode | Number of<br>Clocks | Notes         |

|--------------------------------------|----------|-----------------|---------------------|---------------|

| Memory Parametric Dot Product—Single | VDPS     | 4F3(RA)         | 10 + 8 • N          | Interruptable |

| Memory Parametric Dot Product—Double | VDPD     | 4F1(RA)         | 10+16 • N           | Interruptable |

| 3 x 3 Register Dot Product           | R3DP     | 4F03            | 6                   |               |

| Double Precision Multiply Accumulate | MACD     | 4F02            | 8                   |               |

| Polynomial                           | POLY     | 4F06            | 7 • N - 2           |               |

| Clear Accumulator                    | CLAC     | 4F00            | 4                   |               |

| Store Accumulator (32-Bit)           | STA      | 4F08            | 7                   |               |

| Store Accumulator (48-Bit)           | STAL     | 4F04            | 11                  |               |

| Load Accumulator (32-Bit)            | LAC      | 4F05            | 9                   |               |

| Load Accumulator Long (48-Bit)       | LACL     | 4F07            | 9                   |               |

| Move MMU Page Block                  | MMPG     | 4F0F            | 16+8 • N            | Privileged    |

| Load Timer A Reset Register          | LTAR     | 4F0D            | 4                   |               |

| Load Timer B Reset Register          | LTBR     | 4F0E            | 4                   |               |

## ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Supply Voltage Range                    | -0.5V to 7.0V                   |

|-----------------------------------------|---------------------------------|

| Input Voltage Range                     | -0.5V to V <sub>CC</sub> + 0.5V |

| Storage Temperature Range               | -65°C to + 150°C                |

| Input Current Range                     | -30mA to +5mA                   |

| Voltage Applied to Inputs               | -0.5V to VCC + 0.5V             |

| Current Applied to Outputs <sup>3</sup> | 150 mA                          |

| Maximum Power Dissipation <sup>2</sup>  | 1.5W                            |

| Operating worst case power dissipation (outputs open), Note 4: |                |  |  |  |

|----------------------------------------------------------------|----------------|--|--|--|

| Device type 05 (20 MHz)                                        | 0.4W at 20 MHz |  |  |  |

| Device type 06 (30 MHz)                                        | 0.5W at 30 MHz |  |  |  |

| Device type 07 (40 MHz)                                        | 0.6W at 40 MHz |  |  |  |

Lead Temperature Range 300° C (soldering 10 seconds)

| Thermal resistance, junction-to-case ( $\Theta_{JC}$ ), Note 5: |       |  |  |  |

|-----------------------------------------------------------------|-------|--|--|--|

| Cases X and T                                                   | 8°C/W |  |  |  |

| Cases Y and U                                                   | 5°C/W |  |  |  |

| Case Z                                                          | 6°C/W |  |  |  |

# RECOMMENDED OPERATING CONDITIONS

| Supply Voltage Range                | 4.5V to 5.5V    |

|-------------------------------------|-----------------|

| Case Operating Temperature<br>Range | -55°C to +125°C |

#### NOTE 1:

Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability.

#### NOTE 2:

Must withstand the added power dissipation due to short circuit test e.g.,  $\mathsf{I}_{\text{OS}}$

#### NOTE 3:

Duration one second or less.

#### NOTE 4: Device Type Definitions from 5962-87665 SMD:

Device Type 05: 20 MHz Device Type 06: 30 MHz Device Type 07: 40 MHz

#### NOTE 5: Case Definitions from 5962-87665 SMD:

Case X: Dual In-Line

Case T: Dual In-Line with Gull-Wing Leads

Case Y: Leaded Chip Carrier with Gull-Wing Leads

Case U: Leaded Chip Carrier with Unformed Leads

Case Z: Pin Grid Array

## DC ELECTRICAL SPECIFICATIONS (Over recommended operating conditions)

| Symbol            | Parameter                                                                            |                | Min                   | Max                   | Unit | Cond                                                                                       | itions <sup>1</sup>      |

|-------------------|--------------------------------------------------------------------------------------|----------------|-----------------------|-----------------------|------|--------------------------------------------------------------------------------------------|--------------------------|

| V <sub>IH</sub>   | Input HIGH Level Voltag                                                              | je             | 2.0                   | V <sub>CC</sub> + 0.5 | V    |                                                                                            |                          |

| V <sub>IL</sub>   | Input LOW Level Voltag                                                               | e <sup>2</sup> | -0.5                  | 0.8                   | V    |                                                                                            |                          |

| V <sub>CD</sub>   | Input Clamp Diode Volta                                                              | age            |                       | -1.2                  | V    | V <sub>CC</sub> = 4.5V, I <sub>IN</sub> = -18mA                                            |                          |

| V                 | Output HIGH Level Voltage                                                            |                | 2.4                   |                       | V    | $V_{CC} = 4.5V$                                                                            | I <sub>OH</sub> = -8.0mA |

| V <sub>OH</sub>   |                                                                                      | aye            | V <sub>CC</sub> - 0.2 |                       | V    | $V_{CC} = 4.5V$                                                                            | I <sub>OH</sub> = -300μA |

| Va                | Output LOW Level Volta                                                               | 200            |                       | 0.5                   | V    | $V_{CC} = 4.5V$                                                                            | I <sub>OL</sub> = 8.0mA  |

| V <sub>OL</sub>   |                                                                                      | age            |                       | 0.2                   | V    | $V_{CC} = 4.5V$                                                                            | I <sub>OL</sub> = 300μA  |

| I <sub>IH1</sub>  | Input HIGH Level Curre<br>except $IB_0 - IB_{15}$ ,<br>BUS BUSY, BUS LOCK            |                |                       | 10                    | μA   | $V_{IN} = V_{CC}, V_{CC} = 5.5V$                                                           |                          |

| I <sub>IH2</sub>  | Input HIGH Level Curre<br>IB <sub>0</sub> – IB <sub>15</sub> ,<br>BUS BUSY, BUS LOCH |                |                       | 50                    | μA   | V <sub>IN</sub> = V <sub>CC</sub> , V <sub>CC</sub> = 5.5V                                 |                          |

| I <sub>IL1</sub>  | Input LOW Level Curren<br>except $IB_0 - IB_{15}$ ,<br>BUS BUSY, BUS LOCH            |                |                       | -10                   | μA   | $V_{IN} = GND, V_{CC} = 5.5V$                                                              |                          |

| I <sub>IL2</sub>  | Input LOW Level Current IB <sub>0</sub> – IB <sub>15</sub> , BUS BUSY, BUS LOCK      |                |                       | -50                   | μA   | V <sub>IN</sub> = GND, V <sub>CC</sub> = 5.5V                                              |                          |

| I <sub>OZH</sub>  | Output Three-State Cur                                                               | rent           |                       | 50                    | μA   | V <sub>OUT</sub> = 2.4V, V <sub>CC</sub> = 5.5V                                            |                          |

| I <sub>OZL</sub>  | Output Three-State Cur                                                               | rent           |                       | -50                   | μA   | $V_{OUT} = 0.5V, V_{CC} = 5.5V$                                                            |                          |

| Iccac             | Quiescent Power Suppl<br>Current (CMOS Input<br>Levels)                              | y              |                       | 20                    | mA   | $V_{IN} < 0.2V \text{ or } < V_{CC} - 0.2V,$<br>f = 0MHz, Outputs Open,<br>$V_{CC} = 5.5V$ |                          |

| I <sub>CCQT</sub> | Quiescent Power Suppl<br>Current (TTL Input<br>Levels)                               | y              |                       | 50                    | mA   | $V_{IN} < 3.4V$ , f = 0MHz,<br>Outputs Open,<br>$V_{CC} = 5.5V$                            |                          |

|                   | Dynamic Power                                                                        | 20 MHz         |                       | 70                    | mA   | $V_{IN} = 0V$ to $V_{CC}$ ,                                                                | tr = tf = 2.5 ns,        |

| I <sub>CCD</sub>  | Supply Current                                                                       | 30 MHz         |                       | 85                    | mA   | Outputs Open,                                                                              |                          |

|                   |                                                                                      | 40 MHz         |                       | 100                   | mA   | $V_{CC} = 5.5V$                                                                            |                          |

| I <sub>OS</sub>   | Output Short Circuit Current <sup>3</sup>                                            |                | -25                   |                       | mA   | $V_{OUT} = GND, V_{C}$                                                                     | <sub>CC</sub> = 5.5V     |

| C <sub>IN</sub>   | Input Capacitance                                                                    |                |                       | 10                    | pF   |                                                                                            |                          |

| C <sub>OUT</sub>  | Output Capacitance                                                                   |                |                       | 15                    | pF   |                                                                                            |                          |

| C <sub>I/O</sub>  | Bi-directional Capacitan                                                             | се             |                       | 15                    | pF   |                                                                                            |                          |

1.  $4.5V \le V_{CC} \le 5.5V$ ,  $-55^{\circ}C \le T_C \le +125^{\circ}C$ . Unless otherwise specified, testing shall be conducted at worst-case conditions.

2.  $V_{IL} = -3.0V$  for pulse widths less than or equal to 20ns.

3. Duration of the short should not exceed one second; only one output may be shorted at a time.

# SIGNAL PROPAGATION DELAYS<sup>1,2</sup>

|                          |                                                                                                                                           | 20  | MHz      | 30  | MHz      | 40  | MHz      |          |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-----|----------|-----|----------|----------|

| Symbol                   | Parameter                                                                                                                                 | Min | Max      | Min | Max      | Min | Max      | Unit     |

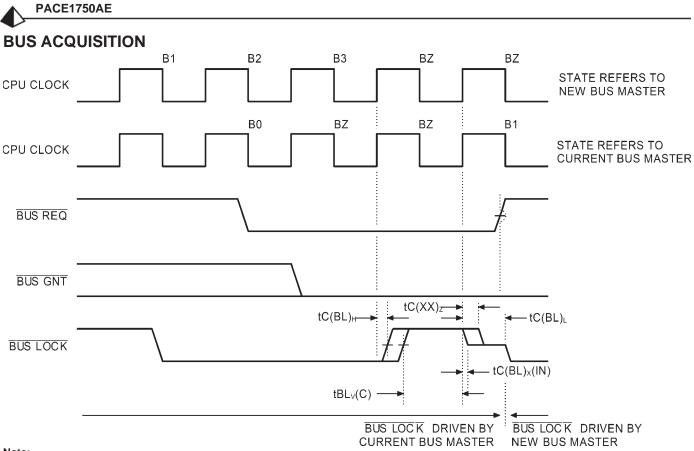

| t <sub>C(BR)L</sub>      | BUS REQ                                                                                                                                   |     | 25       |     | 25       |     | 22       | ns       |

| t <sub>C(BR)H</sub>      | BUS REQ                                                                                                                                   |     | 25       |     | 25       |     | 22       | ns       |

| t <sub>BGV(C)</sub>      | BUS GNT setup                                                                                                                             | 5   |          | 5   |          | 5   |          | ns       |

| t <sub>C(BG)X</sub>      | BUS GNT hold                                                                                                                              | 5   |          | 5   |          | 5   |          | ns       |

| t <sub>C(BB)L</sub>      | BUS BUSY LOW                                                                                                                              |     | 24       |     | 24       |     | 20       | ns       |

| t <sub>C(BB)H</sub>      | BUS BUSY HIGH                                                                                                                             |     | 20       |     | 20       |     | 15       | ns       |

| t <sub>BBV(C)</sub>      | BUS BUSY setup                                                                                                                            | 5   |          | 5   |          | 5   |          | ns       |

| t <sub>C(BB)X</sub>      | BUS BUSY hold                                                                                                                             | 5   |          | 5   |          | 5   |          | ns       |

| t <sub>C(BL)L</sub>      | BUS LOCK LOW                                                                                                                              |     | 25       |     | 25       |     | 21       | ns       |

| t <sub>C(BL)H</sub>      | BUS LOCK HIGH                                                                                                                             |     | 20       |     | 20       |     | 17       | ns       |

| t <sub>BLV(C)</sub>      | BUS LOCK setup                                                                                                                            | 5   |          | 5   |          | 5   |          | ns       |

| t <sub>C(BL)X (IN)</sub> | BUS LOCK hold                                                                                                                             | 5   |          | 5   |          | 5   |          | ns       |

| t <sub>C(ST)V</sub>      | D/ $\overline{I}$ Status, AS <sub>0</sub> -AS <sub>3</sub> , AK <sub>0</sub> -AK <sub>3</sub> ,<br>M/ $\overline{IO}$ , R/ $\overline{W}$ |     | 20<br>25 |     | 20<br>25 |     | 20<br>20 | ns<br>ns |

| t <sub>C(ST)X</sub>      | $M/\overline{IO}$ , $R/\overline{W}$ , $D/\overline{I}$ Status,<br>AS <sub>0</sub> -AS <sub>3</sub> , AK <sub>0</sub> -AK <sub>3</sub>    | 0   |          | 0   |          | 0   |          | ns       |

| t <sub>C(SA)H</sub>      | STRBA HIGH                                                                                                                                |     | 17       |     | 17       |     | 16       | ns       |

| t <sub>C(SA)L</sub>      | STRBA LOW                                                                                                                                 |     | 17       |     | 17       |     | 16       | ns       |

| t <sub>SAL(IBA)X</sub>   | Address hold from STRBA LOW                                                                                                               | 5   |          | 5   |          | 5   |          | ns       |

| t <sub>RAV(C)</sub>      | RDYA setup                                                                                                                                | 5   |          | 5   |          | 5   |          | ns       |

| t <sub>C(RA)X</sub>      | RDYA hold                                                                                                                                 | 5   |          | 5   |          | 5   |          | ns       |

| t <sub>C(SDW)L</sub>     | STR BD LOW write                                                                                                                          |     | 17       |     | 17       |     | 14       | ns       |

| t <sub>C(SD)H</sub>      | STR BD HIGH                                                                                                                               |     | 17       |     | 17       |     | 14       | ns       |

| t <sub>FC(SDR)L</sub>    | STR BD LOW read                                                                                                                           |     | 17       |     | 17       |     | 14       | ns       |

| t <sub>SDRH(IBD)X</sub>  | STR BD HIGH                                                                                                                               | 0   |          | 0   |          | 0   |          | ns       |

| t <sub>SDWH(IBD)X</sub>  | STR BD HIGH                                                                                                                               | 25  |          | 25  |          | 17  |          | ns       |

| t <sub>SDL(SD)H</sub>    | STR BD write                                                                                                                              | 26  |          | 26  |          | 20  |          | ns       |

| t <sub>RDV(C)</sub>      | RDYD setup                                                                                                                                | 5   |          | 5   |          | 5   |          | ns       |

| t <sub>C(RD)X</sub>      | RDYD hold                                                                                                                                 | 5   |          | 5   |          | 5   |          | ns       |

| t <sub>C(IBA)V</sub>     | IB <sub>0</sub> -IB <sub>15</sub>                                                                                                         |     | 25       | ĺ   | 25       |     | 20       | ns       |

| t <sub>FC(IBA)X</sub>    | IB <sub>0</sub> -IB <sub>15</sub>                                                                                                         | 0   |          | 0   |          | 0   |          | ns       |

| t <sub>IBDRV(C)</sub>    | IB <sub>0</sub> -IB <sub>15</sub> setup                                                                                                   | 5   |          | 5   |          | 5   |          | ns       |

| t <sub>C(IBD)X</sub>     | IB <sub>0</sub> -IB <sub>15</sub> hold (read)                                                                                             | 6   |          | 6   |          | 5   |          | ns       |

| t <sub>C(IBD)X</sub>     | Data valid out (write)                                                                                                                    | 0   |          | 0   |          | 0   |          | ns       |

# SIGNAL PROPAGATION DELAYS<sup>1,2</sup> (continued)

|                                        |                                                   | 20  | MHz | 30  | ИHz | 40  | MHz |      |

|----------------------------------------|---------------------------------------------------|-----|-----|-----|-----|-----|-----|------|

| Symbol                                 | Parameter                                         | Min | Max | Min | Max | Min | Max | Unit |

| t <sub>FC(IBD)V</sub>                  | IB <sub>0</sub> -IB <sub>15</sub>                 |     | 25  |     | 25  |     | 20  | ns   |

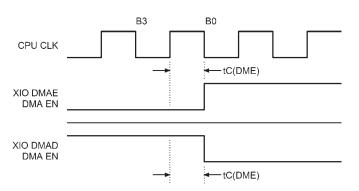

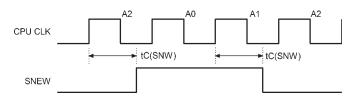

| t <sub>C(SNW)</sub>                    | SNEW                                              |     | 26  |     | 25  |     | 22  | ns   |

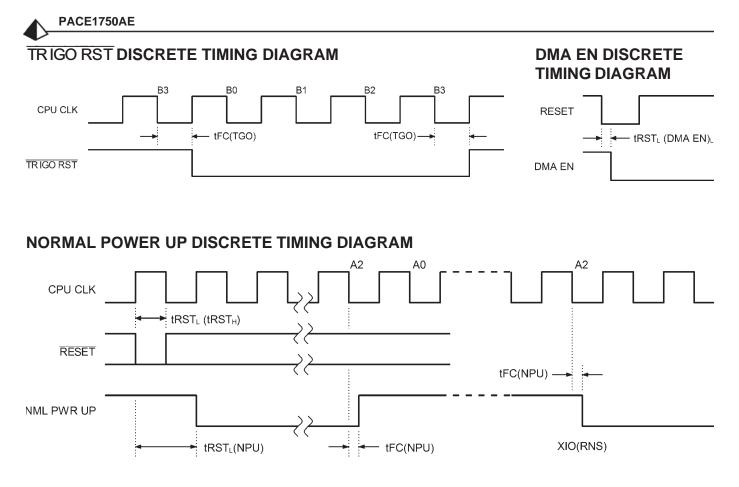

| t <sub>FC(TGO)</sub>                   | TR IGO RST                                        |     | 26  |     | 25  |     | 22  | ns   |

| t <sub>RSTL(DMA ENL)</sub>             | DMA enable                                        |     | 35  |     | 35  |     | 30  | ns   |

| t <sub>C(DME)</sub>                    | DMA enable                                        |     | 35  |     | 35  |     | 30  | ns   |

| t <sub>FC(NPU)</sub>                   | Normal power up                                   |     | 35  |     | 35  |     | 30  | ns   |

| t <sub>C(ER)</sub>                     | Clock to major error unrecoverable                |     | 50  |     | 50  |     | 45  | ns   |

| t <sub>RSTL(NPU)</sub>                 | RESET                                             |     | 40  |     | 40  |     | 30  | ns   |

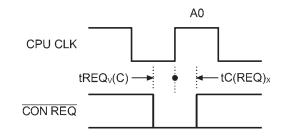

| t <sub>REQV(C)</sub>                   | Console request                                   | 0   |     | 0   |     | 0   |     | ns   |

| t <sub>C(REQ)X</sub>                   | Console request                                   | 10  |     | 10  |     | 10  |     | ns   |

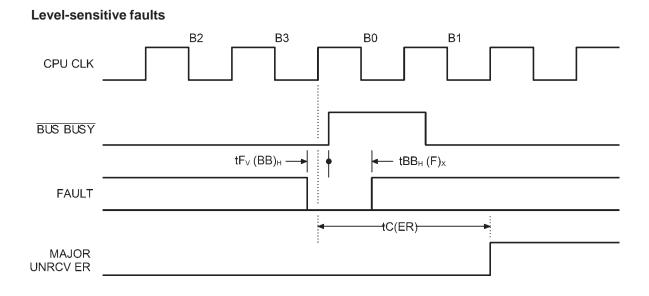

| t <sub>FV(BB)H</sub>                   | Level sensitive faults                            | 5   |     | 5   |     | 5   |     | ns   |

| t <sub>BBH(F)X</sub>                   | Level sensitive faults                            | 5   |     | 5   |     | 5   |     | ns   |

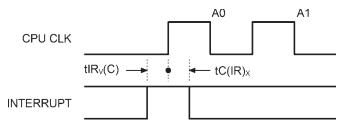

| t <sub>IRV(C)</sub>                    | IOL <sub>1-2</sub> INT user interrupt (0-5) setup | 0   |     | 0   |     | 0   |     | ns   |

| t <sub>C(IR)X</sub>                    | Power down interrupt level sensitive hold         | 10  |     | 10  |     | 10  |     | ns   |

| t <sub>RSTL</sub> (t <sub>RSTH</sub> ) | Reset pulse width                                 | 20  |     | 20  |     | 15  |     | ns   |

| t <sub>C(XX)Z</sub>                    | Clock to three-state                              |     | 17  |     | 17  |     | 13  | ns   |

| t <sub>f(F)</sub> , t <sub>1(1)</sub>  | Edge sensitiive pulse width                       | 5   |     | 5   |     | 5   |     | ns   |

| t <sub>r</sub> , t <sub>f</sub>        | Clock rise and fall                               |     | 5   |     | 5   |     | 5   | ns   |

#### Notes

1.  $4.5V \le V_{CC} \le 5.5V$ ,  $-55^{\circ}C \le T_{C} \le +125^{\circ}C$ . Unless otherwise specified, testing shall be conducted at worst-case conditions.

2. All timing parameters are composed of Three elements. The first "t" stands for timing. The second represents the "from" signal. The third in parentheses indicates "to" signal. When the CPU clock is one of the signal elements, either the rising edge "C" or the falling edge "FC" is referenced. When other elements are used, an additional suffix indicates the final logic level of the signal. "L" - low level, "H" - high level, "V" - valid, "Z" - high impedance, "X" - don't care, "LH" - low to high, "ZH" - high impedance to high, "R" - read cycle, and "W" - write cycle.

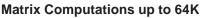

## MINIMUM WRITE BUS CYCLE TIMING DIAGRAM

#### Note:

#### Note:

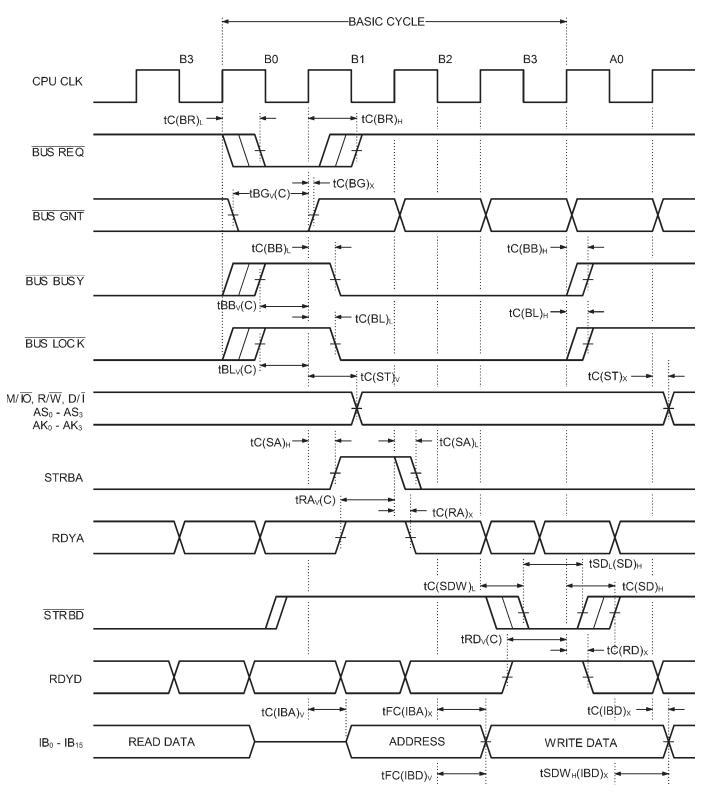

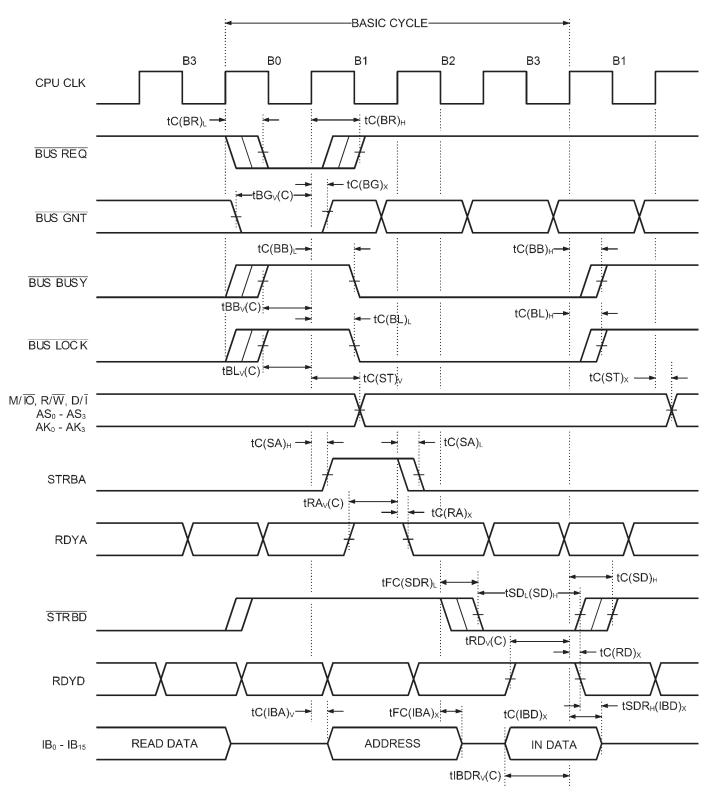

## MINIMUM WRITE BUS CYCLE, FOLLOWED BY A NON-BUS CYCLE, TIMING DIAGRAM

#### Note:

## **XIO OPERATIONS**

## SNEW DISCRETE TIMING DIAGRAM

#### Note:

## EXTERNAL FAULTS AND INTERRUPTS TIMING DIAGRAM

Edge-sensitive interrupts and faults (SYSFLT $_0$ , SYSFLT $_1$ ) min. pulse width

# ↓ tF(F) tl(l)

#### Level-sensitive interrupts

Note: tC(IR)<sub>X</sub> max = 35 clocks

## **CON REQ**

#### Note:

#### Note:

A CPU contending for the BUS will assert the BUS REQ line, and will acquire it when BUS GNT is asserted and the BUS is not locked (BUS LOCK is high).

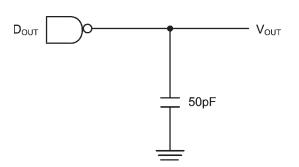

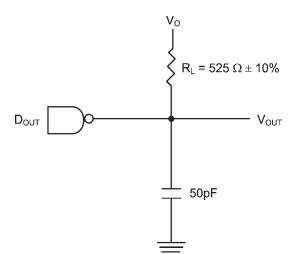

## SWITCHING TIME TEST CIRCUITS

#### Standard Output (Non-Three-State)

Three-State

#### Note:

| Parameter        | V0                 | VMEA            |

|------------------|--------------------|-----------------|

| t <sub>PLZ</sub> | ≥ 3V               | 0.5V            |

| t <sub>PHZ</sub> | 0V                 | $V_{CC} - 0.5V$ |

| t <sub>PXL</sub> | V <sub>CC</sub> /2 | 1.5V            |

| t <sub>PXH</sub> | V <sub>CC</sub> /2 | 1.5V            |

## SIGNAL DESCRIPTIONS

## **CLOCKS AND EXTERNAL REQUESTS**

| Mnemonic       | Name            | Description                                                                                                                                                               |

|----------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU CLK        | CPU clock       | A single phase input clock signal (0-40 MHz, 40 percent to 60 percent duty cycle.                                                                                         |

| TIMER CLK      | Timer clock     | A 100 KHz input that, after synchronization with CPU CLK, provides the clock for timer A and timer B. If timers are used, the CPU CLK signal frequency must be > 300 KHz. |

| RESET          | Reset           | An active low input that initializes the device.                                                                                                                          |

| <b>CON REQ</b> | Console request | An active low input that initiates console operations after completion of the current instruction.                                                                        |

## INTERRUPT INPUTS

| Mnemonic               | Name                 | Description                                                                                                                                                                                                |

|------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWRDN INT              | Power down interrupt | An interrupt request input that cannot be masked or disabled. This signal<br>is active on the positive going edge or the high level, according to the<br>interrupt mode bit in the configuration register. |

| USR₀INT -<br>USR₅INT   | User interrupt       | Interrupt request input signals that are active on the positive going edge edge or the high level, according to the interrupt mode bit in the configuration register.                                      |

| IOL <sub>1</sub> INT - | I/O level interrupts | Active high interrupt request inputs that can be used to expand the number of user interrupts.                                                                                                             |

| IOL2INT                |                      |                                                                                                                                                                                                            |

#### FAULTS

| Mnemonic                                   | Name                                                       | Description                                                                                                                                                                  |

|--------------------------------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MEM PRTER                                  | Memory protect error                                       | An active low input generated by the MMU or BPU, or both and sampled<br>by the BUS BUSY signal into the Fault Register (bit 0 CPU bus cycle, bit<br>1 if non-CPU bus cycle). |

| MEM PAR ER                                 | Memory parity error                                        | An active low input sampled by the $\overline{\mbox{BUSY}}$ signal into bit 2 of the fault register.                                                                         |

| EXT ADR ER                                 | External address error                                     | An active low input sampled by the $\overline{\text{BUS BUS Y}}$ signal into the Fault register (bit 5 or 8), depending on the cycle (memory or I/O).                        |

| SYSFLT <sub>0</sub><br>SYSFLT <sub>1</sub> | System fault <sub>0</sub> ,<br>System fault <sub>1</sub> , | Asynchronous, positive edge-sensitive inputs that set bit 7 (SYSFLT <sub>0</sub> ) or bits 13 and 15 (SYSFLT <sub>1</sub> ) in the Fault register.                           |

#### ERROR CONTROL

| Mnemonic | Name                | Description                                                                                  |

|----------|---------------------|----------------------------------------------------------------------------------------------|

| UNRCV ER | Unrecoverable error | An active high output that indicates the occurrence of an error classified as unrecoverable. |

| MAJ ER   | Major error         | An active high output that indicates the occurrence of an error classified as major.         |

# SIGNAL DESCRIPTIONS (Continued)

## **BUS CONTROL**

| Mnemonic         | Name                | Description                                                                                                                                                                                                                                                                                     |

|------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D/Ī              | Data or instruction | An output signal that indicates whether the current bus cycle access is for Data (HIGH) or Instruction (LOW). It is three-state during bus cycles not assigned to the CPU. This line can be used as an additional memory address bit for systems that require separate data and program memory. |

| R/W              | Read or write       | An output signal that indicates direction of data flow with respect to the current bus master. A HIGH indicates a read or input operation and a LOW indicates a write or output operation. The signal is three-state during bus cycles not assigned to the CPU.                                 |

| M/ <del>IO</del> | Memory or I/O       | An output signal that indicates whether the current bus cycle is memory (HIGH) or I/O (LOW). This signal is three-state during bus cycles not assigned to the CPU.                                                                                                                              |

| STRBA            | Address strobe      | An active HIGH output that can be used to externally latch the memory or I/O address at the HIGH-to-LOW transition of the strobe. The signal is three-state during bus cycles not assigned to the CPU.                                                                                          |

| RDYA             | Address ready       | An active HIGH input that can be used to extend the address phase of a bus cycle. When RDYA is not active, wait states are inserted by the device to accommodate slower memory or I/O devices.                                                                                                  |

| STRBD            | Data strobe         | An active LOW output that can be used to strobe data in memory and XIO cycles. This signal is three-state during bus cycles not assigned to the CPU.                                                                                                                                            |

| RDYD             | Data ready          | An active HIGH input that extends the data phase of a bus cycle. When RDYD is not active, wait states are inserted by the device to accommodate slower memory or I/O devlces.                                                                                                                   |

## **INFORMATION BUS**

| Mnemonic                           | Name            | Description                                                                                                                                          |  |

|------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IB <sub>0</sub> - IB <sub>15</sub> | Information bus | A bidirectional time-multiplexed address/data bus that is three-state during bus cycles not assigned to the CPU. $IB_0$ is the most significant bit. |  |

## STATUS BUS

| Mnemonic                          | Name          | Description                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| АК <sub>0</sub> - АК <sub>3</sub> | Access key    | Outputs used to match the access lock in the MMU for memory accesses<br>(a mismatch will cause the MMU to pull the $\overline{\text{MEM PRT ER}}$ signal LOW),<br>and also indicates processor state (PS). Privileged instructions can be<br>executed with PS = 0 only. These signals are three-state during bus<br>cycles not assigned to the CPU.           |

| AS <sub>0</sub> - AS <sub>3</sub> | Address state | Outputs that select the page register group in the MMU. It is three-state during bus cycles not assigned to the CPU. These outputs together with $D/\bar{I}$ can be used to expand the device direct addressing space to 4 MBytes, in a nonprotected mode (no MMU). However, using this addressing mode may produce situations not specified in MIL-STD-1750. |

## SIGNAL DESCRIPTIONS (Continued)

## **BUS ARBITRATION**

| Mnemonic | Name        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUS REQ  | Bus request | An active LOW output that indicates the CPU requires the bus. It becomes inactive when the CPU has acquired the bus and started the bus cycle.                                                                                                                                                                                                                                                                                                                                                 |

| BUS GNT  | Bus grant   | An active LOW input from an external arbiter that indicates the CPU currently has the highest priority bus request. If the bus is not used and not locked, the CPU may begin a bus cycle, commencing with the next CPU clock. A HIGH level will hold the CPU in Hi-Z state (Bz), three-stating the IB bus status lines (D/ $\overline{I}$ , R/ $\overline{W}$ , M/ $\overline{IO}$ ), strobes (STRBA, STRBD), and all the other lines that go three-state when this CPU does not have the bus. |

| BUS BUSY | Bus busy    | An active LOW, bidirectional signal used to establish the beginning and<br>end of a bus cycle. The trailing edge (LOW-to-HIGH transition) is used<br>for sampling bits into the fault register. It is three-state in bus cycles not<br>assigned to this CPU. However, the CPU monitors the BUS BUSY line<br>for latching non-CPU bus cycle faults into the fault register.                                                                                                                     |

| BUS LOCK | Bus lock    | An active low, bi-directional signal used to lock the bus for successive<br>bus cycles. During non-locked bus cycles, the BUS LOCK signal mimics<br>the BUS BUSY signal. It is three-state during bus cycles not assigned to<br>the CPU. The following instructions will lock the bus: INCM, DECM, SB,<br>RB, TSB, SRM, STUB and STLB.                                                                                                                                                         |

#### **DISCRETE CONTROL**

| Mnemonic   | Name                           | Description                                                                                                                                                                                 |

|------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMA EN     | Direct memory<br>Access enable | An active HIGH output that indicates the DMA is enabled. It is disabled when the CPU is initialized (reset) and can be enabled or disabled under program control (I/O commands DMAE, DMAD). |

| NML PWRUP  | Normal power up                | An active HIGH output that is set when the CPU has successfully completed the built-in self test in the initialization sequence. It can be reset by the I/O command RNS.                    |

| SNEW       | Start new                      | An active HIGH output that indicates a new instruction is about to start executing in the next cycle.                                                                                       |

| TR IGO RST | Trigger-go reset               | An active LOW discrete output. This signal can be pulsed low under program control I/O address 400B (Hex) and is automatically pulsed during processor initialization.                      |

## **TERMINAL CONNECTIONS**

## Case Outline: Pin Grid Array (Case Z)

| Terminal<br>Number | Terminal<br>Symbol | Terminal<br>Number | Terminal<br>Symbol | Terminal<br>Number | Terminal<br>Symbol   |

|--------------------|--------------------|--------------------|--------------------|--------------------|----------------------|

| B1                 | V <sub>CC</sub>    | L5                 | DMA EN             | D11                | AS <sub>1</sub>      |

| B2                 | IB <sub>14</sub>   | K5                 | CON REQ            | D10                | AS <sub>2</sub>      |

| C1                 | IB <sub>13</sub>   | L6                 | V <sub>CC</sub>    | C11                | AS <sub>3</sub>      |

| C2                 | IB <sub>12</sub>   | K6                 | SNEW               | C10                | IOL <sub>2</sub> INT |

| D1                 | IB <sub>11</sub>   | L7                 | BUS LOCK           | B11                | V <sub>CC</sub>      |

| D2                 | IB <sub>10</sub>   | K7                 | BUS GNT            | A10                | GND                  |

| E1                 | IB <sub>9</sub>    | L8                 | BUS BUSY           | B10                | IOL <sub>1</sub> INT |

| E2                 | IB <sub>8</sub>    | K8                 | M/TO               | A9                 | USR <sub>5</sub> INT |

| F1                 | GND                | L9                 | D/Ī                | B9                 | USR₄INT              |

| F2                 | IB <sub>7</sub>    | K9                 | R/W                | A8                 | USR <sub>3</sub> INT |

| G1                 | IB <sub>6</sub>    | L10                | GND                | B8                 | USR <sub>2</sub> INT |

| G2                 | IB <sub>5</sub>    | K11                | RDYD               | A7                 | USR <sub>1</sub> INT |

| H1                 | IB <sub>4</sub>    | K10                | RDYA               | B7                 | USR <sub>0</sub> INT |

| H2                 | IB <sub>3</sub>    | J11                | BUS REQ            | A6                 | PWRDN INT            |

| J1                 | IB <sub>2</sub>    | J10                | STRBD              | B6                 | GND                  |

| J2                 | IB <sub>1</sub>    | H11                | STRBA              | A5                 | MAJ ER               |

| K1                 | IB <sub>0</sub>    | H10                | CPU CLK            | B5                 | SYSFLT1              |

| L2                 | GND                | G11                | AK <sub>0</sub>    | A4                 | SYSFLT <sub>0</sub>  |

| K2                 | UNRCV ER           | G10                | AK <sub>1</sub>    | B4                 | EXT ADR ER           |

| L3                 | TIMER CLK          | F11                | AK <sub>2</sub>    | A3                 | MEM PAR ER           |

| K3                 | NML PWRUP          | F10                | AK <sub>3</sub>    | B3                 | MEM PRT ER           |

| L4                 | RESET              | E11                | GND                | A2                 | IB <sub>15</sub>     |

| K4                 | TRIGO RST          | E10                | AS <sub>0</sub>    |                    |                      |

## **TERMINAL CONNECTIONS**

Case Outlines: Leaded Chip Carrier with unformed leads (Case U) and Leaded Chip Carrier with Gull-Wing Leads (Case Y)

| Terminal<br>Number | Terminal<br>Symbol | Terminal<br>Number | Terminal<br>Symbol   | Terminal<br>Number | Terminal<br>Symbol |

|--------------------|--------------------|--------------------|----------------------|--------------------|--------------------|

| 1                  | GND                | 23                 | IB <sub>11</sub>     | 46                 | AS <sub>2</sub>    |

| 2                  | CON REQ            | 24                 | IB <sub>12</sub>     | 47                 | AS <sub>1</sub>    |

| 3                  | DMA EN             | 25                 | IB <sub>13</sub>     | 48                 | AS <sub>0</sub>    |

| 4                  | TR IGO RST         | 26                 | IB <sub>14</sub>     | 49                 | GND                |

| 5                  | RESET              | 27                 | IB <sub>15</sub>     | 50                 | AK <sub>3</sub>    |

| 6                  | NML PWRUP          | 28                 | MEM PRT ER           | 51                 | AK <sub>2</sub>    |

| 7                  | TIMER CLK          | 29                 | MEM PAR ER           | 52                 | VCC                |

| 8                  | UNRCV ER           | 30                 | EXT ADR ER           | 53                 | AK <sub>1</sub>    |

| 9                  | GND                | 31                 | SYSFLT0              | 54                 | AK <sub>0</sub>    |

| 10                 | IB <sub>0</sub>    | 32                 | SYSFLT1              | 55                 | CPU CLK            |

| 11                 | IB <sub>1</sub>    | 33                 | MAJ ER               | 56                 | STRBA              |

| 12                 | IB <sub>2</sub>    | 34                 | GND                  | 57                 | STRBD              |

| 13                 | IB <sub>3</sub>    | 35                 | VCC                  | 58                 | BUS REQ            |

| 14                 | IB <sub>4</sub>    | 36                 | PWRDN INT            | 59                 | RDYA               |

| 15                 | IB <sub>5</sub>    | 37                 | USR <sub>0</sub> INT | 60                 | RDYD               |

| 16                 | IB <sub>6</sub>    | 38                 | USR <sub>1</sub> INT | 61                 | R/W                |

| 17                 | IB <sub>7</sub>    | 39                 | USR <sub>2</sub> INT | 62                 | D/Ī                |

| 18                 | GND                | 40                 | USR <sub>3</sub> INT | 63                 | M/ĪO               |

| 19                 | IB <sub>8</sub>    | 41                 | USR <sub>4</sub> INT | 64                 | BUS BUSY           |

| 20                 | IB <sub>9</sub>    | 42                 | USR <sub>5</sub> INT | 65                 | BUS GNT            |

| 21                 | VCC                | 43                 | IOL <sub>1</sub> INT | 66                 | BUS LOCK           |

| 22                 | IB <sub>10</sub>   | 44                 | IOL <sub>2</sub> INT | 67                 | SNEW               |

|                    |                    | 45                 | AS <sub>3</sub>      | 68                 | VCC                |

PACE1750AE

## **TERMINAL CONNECTIONS**

| Case Outlines: Dual-In-Line (Case X) and Dual-In-Line with Gull-Wing Leads (Case T) |                    |                    |                      |                    |                    |

|-------------------------------------------------------------------------------------|--------------------|--------------------|----------------------|--------------------|--------------------|

| Terminal<br>Number                                                                  | Terminal<br>Symbol | Terminal<br>Number | Terminal<br>Symbol   | Terminal<br>Number | Terminal<br>Symbol |

| 1                                                                                   | GND                | 23                 | IB <sub>13</sub>     | 44                 | AS <sub>1</sub>    |

| 2                                                                                   | <b>CON REQ</b>     | 24                 | IB <sub>14</sub>     | 45                 | AS <sub>0</sub>    |

| 3                                                                                   | DMA EN             | 25                 | IB <sub>15</sub>     | 46                 | GND                |

| 4                                                                                   | TR IGO RST         | 26                 | MEM PRT ER           | 47                 | AK <sub>3</sub>    |

| 5                                                                                   | RESET              | 27                 | MEM PAR ER           | 48                 | AK <sub>2</sub>    |

| 6                                                                                   | NML PWRUP          | 28                 | EXT ADR ER           | 49                 | AK <sub>1</sub>    |

| 7                                                                                   | TIMER CLK          | 29                 | SYSFLT0              | 50                 | AK <sub>0</sub>    |

| 8                                                                                   | UNRCV ER           | 30                 | SYSFLT1              | 51                 | CPU CLK            |

| 9                                                                                   | IB <sub>0</sub>    | 31                 | MAJ ER               | 52                 | STRBA              |

| 10                                                                                  | IB <sub>1</sub>    | 32                 | GND                  | 53                 | STRBD              |

| 11                                                                                  | IB <sub>2</sub>    | 33                 | PWRDN INT            | 54                 | BUS REQ            |

| 12                                                                                  | IB <sub>3</sub>    | 34                 | USR <sub>0</sub> INT | 55                 | RDYA               |

| 13                                                                                  | IB <sub>4</sub>    | 35                 | USR <sub>1</sub> INT | 56                 | RDYD               |

| 14                                                                                  | IB <sub>5</sub>    | 36                 | USR <sub>2</sub> INT | 57                 | R/W                |

| 15                                                                                  | IB <sub>6</sub>    | 37                 | USR <sub>3</sub> INT | 58                 | D/Ī                |

| 16                                                                                  | IB <sub>7</sub>    | 38                 | USR <sub>4</sub> INT | 59                 | M/TO               |

| 17                                                                                  | IB <sub>8</sub>    | 39                 | USR <sub>5</sub> INT | 60                 | BUS BUSY           |

| 18                                                                                  | IB <sub>9</sub>    | 40                 | IOL <sub>1</sub> INT | 61                 | BUS GNT            |

| 19                                                                                  | VCC                | 41                 | IOL <sub>2</sub> INT | 62                 | BUS LOCK           |

| 20                                                                                  | IB <sub>10</sub>   | 42                 | AS <sub>3</sub>      | 63                 | SNEW               |

| 21                                                                                  | IB <sub>11</sub>   | 43                 | AS <sub>2</sub>      | 64                 | VCC                |

| 22                                                                                  | IB <sub>12</sub>   |                    |                      |                    |                    |

PACE1750AE

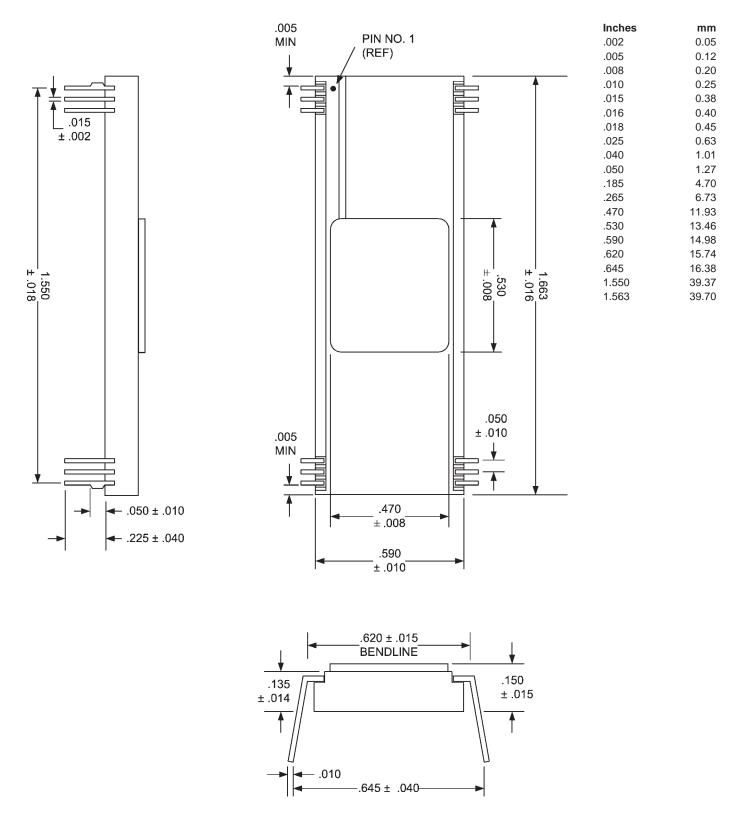

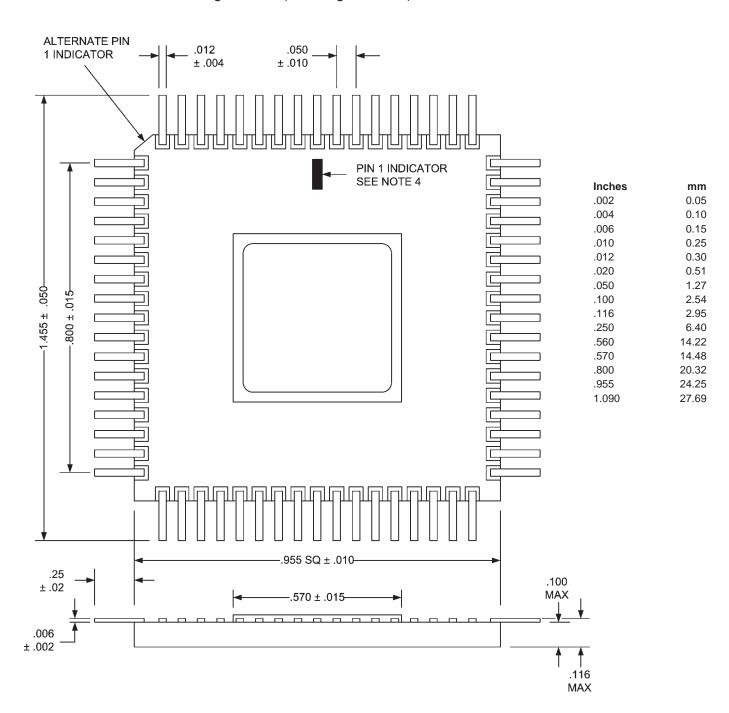

## CASE OUTLINE X:

64 Lead Top Brazed DIP Package, Straight Lead Version (Ordering Code C)

#### NOTES:

1) Dimensions are in inches.

2) Metric equivalents are given for general information only.

3) Unless otherwise specified, tolerances are .02 (0.5 mm) for two place decimals and .005 (0.13 mm) for three place decimals.

## CASE OUTLINE T:

64 Lead Top Brazed DIP Package, Gullwing Lead Version (Ordering Code G)

#### NOTES:

1) Dimensions are in inches.

- 2) Metric equivalents are given for general information only.

- 3) Unless otherwise specified, tolerances are .02 (0.5 mm) for two place decimals and .005 (0.13 mm) for three place decimals.

- 4) Case T is derived from Case X by forming the leads to the shown gullwing configuration.

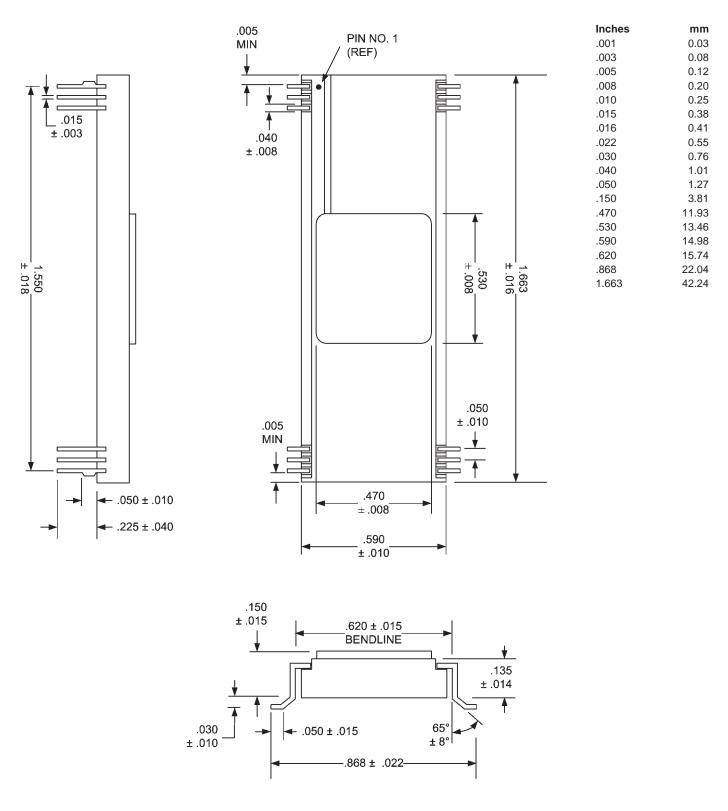

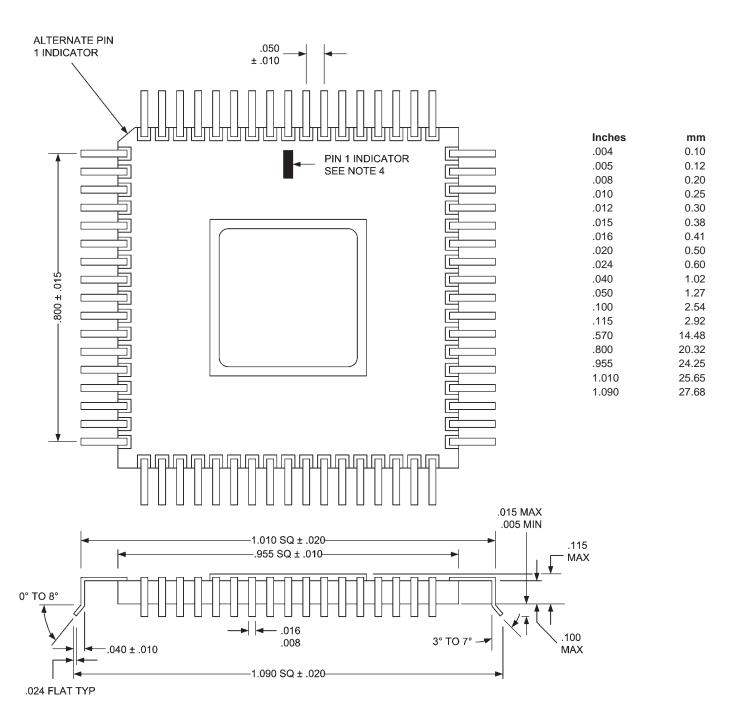

## CASE OUTLINE U:

68 Lead Quad Pack with Straight Leads (Ordering Code QL)

#### NOTES:

- 1) Dimensions are in inches.

- 2) Metric equivalents are given for general information only.

- 3) Unless otherwise specified, tolerances are .02 (0.5 mm) for two place decimals and .005 (0.13 mm) for three place decimals.

4) Pin 1 indicator can be either rectangle, dot, or triangle at specified location or referenced to the uniquely beveled corner.

5) Corners indicated as notched may be either notched or square.

## CASE OUTLINE Y:

68 Lead Quad Pack with Gullwing Leads (Ordering Code QG)

#### NOTES:

- 1) Dimensions are in inches.

- 2) Metric equivalents are given for general information only.

- 3) Unless otherwise specified, tolerances are .02 (0.5 mm) for two place decimals and .005 (0.13 mm) for three place decimals.

- 4) Pin 1 indicator can either be rectangle, dot, or triangle at specified location or referenced to the uniquely beveled corner.

- 5) Corners indicated as notched my be either notched or square (with radius).

- 6) Case Y is derived from Case U by forming the leads to the shown gullwing configuration.

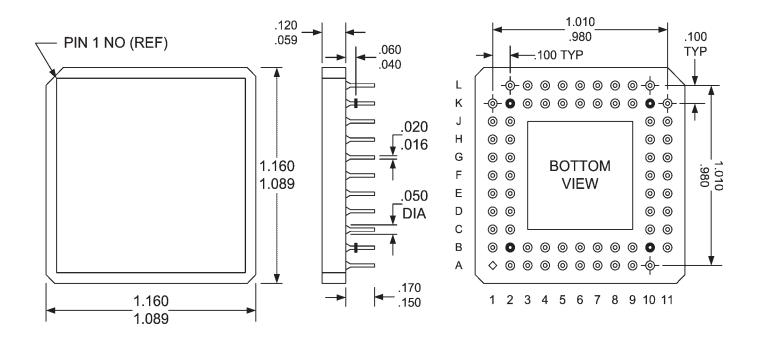

# CASE OUTLINE Z:

68-Pin Pin Grid Array (PGA) (Ordering Code PG)

| Inches | mm    |

|--------|-------|

| .016   | 0.41  |

| .020   | 0.50  |

| .040   | 1.01  |

| .050   | 1.27  |

| .059   | 1.49  |

| .060   | 1.52  |

| .098   | 2.49  |

| .100   | 2.54  |

| .120   | 3.04  |

| .150   | 3.81  |

| .170   | 4.32  |

| 1.010  | 25.65 |

| 1.089  | 27.66 |

| 1.160  | 29.46 |

#### NOTES:

- 1) Dimensions are in inches.

- 2) Metric equivalents are given for general information only.

- 3) Unless otherwise specified, tolerances are .02 (0.5 mm) for two place decimals and .005 (0.13 mm) for three place decimals.

- 4) Corners except pin number 1 (ref.) can be either rounded or square.

- 5) All pins must be on the .100" grid.

## REVISIONS

| DOCUMENT NUMBER:<br>DOCUMENT TITLE: |               | MICRO-2<br>PACE17  | 2<br>50AE CMOS 16-BIT PROCESSOR                                                                                                                                                                                |

|-------------------------------------|---------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REV.                                | ISSUE<br>DATE | ORIG. OF<br>CHANGE | DESCRIPTION OF CHANGE                                                                                                                                                                                          |

| ORIG                                | May-89        | RKK                | New Data Sheet                                                                                                                                                                                                 |

| А                                   | Jun-04        | JDB                | Added Pyramid logo                                                                                                                                                                                             |

| В                                   | Jan-05        | JDB                | Added 20 MHz speed                                                                                                                                                                                             |

| С                                   | Feb-05        | JDB                | Added thermal data (page 3), top brazed package drawing (page 19), and corrected errors on page 2.                                                                                                             |

| D                                   | Mar-05        | DAB                | Added clarification to page 3, corrected Terminal Connections (pages 16-18)                                                                                                                                    |

| E                                   | Apr-05        | JDB                | Removed 35 MHz device.                                                                                                                                                                                         |

| F                                   | Aug-05        | JDB                | Redrew timing diagrams and corrected the following symbols in the signal propagation delay table:<br>1) t <sub>(SDR)HIDX</sub> to t <sub>SDRH(IBD)X</sub><br>2) t <sub>FC(IBA)V</sub> to t <sub>FC(IBA)X</sub> |

| G                                   | Oct-05        | JDB                | Altered case outline drawing for case X and case T                                                                                                                                                             |